# Improving testability during the PCB design process with XJTAG's New Design Gateway Plugin

Simon Payne CEO, XJTAG

Zuken Innovation World 2018

XJTAG © Copyright 2018

本講演では、XJTAG社が提供するDesign Gateway用のプラグインで、時間とコストを削減できることについて紹介します。 まずはじめに、JTAGバウンダリースキャンテストについて説明します。

講演タイトル:「回路設計段階でテスト容易化を支援するDesign GatewayのXJTAG無料プラグイン」

講演概要:BGAなどのプローブアクセスが困難な実装検査の課題を解決する JTAG バウンダリスキャンテストが注目されています。これを最大限に活用するには、MPU、FPGA 等のJTAG 搭載デバイスが正しく接続されることに加え、カバレッジを最大限に引き出す設計上の工夫が求められます。 XJTAG社の無料プラグインは、専門知識が無くても回路設計段階でテスト容易化設計を支援し、手戻りを防ぎ、量産化プロセスを改善することに貢献します。

Get JTAG right – right from the start

**Use JTAG more**

Free Stuff!

Zuken Innovation World 2018

XJTAG © Copyright 2018

特にお伝えしたいことは、次の3点です。

- ・早期段階からJTAGを考慮することの利点

- ・JTAGの利用範囲を広げること

- ・それを支援する無償ツールについて

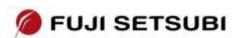

それではJTAGについて、簡単に紹介します。

JTAGを使用することで、他のツールでは不可能なデバイス上のピンに対しても、アクセスして制御できるようになります。

JTAGにはおよそ30年の歴史がありますが、あまり理解されないまま、その用途は限られてきました。

一般にはデバッガインターフェイスとして利用されています。しかしながら他にもテスト、インサーキットプログラミングなど、合計3種の用途があります。

- JTAGはプロセッサ、FPGA、CPLD内に組み込まれているため、ほとんどのPCB上に存在しています。

- それゆえ何か特別なことをしなくても、利用することができます。

- とはいえ、それを最大限に活用できているでしょうか?

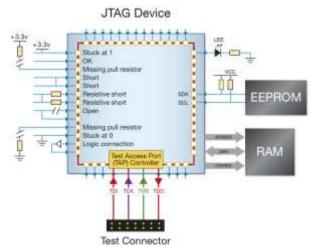

### JTAG / Boundary Scan / 1149.x

#### Designed to minimise access difficulties

- Test Access Port interface is 4/5 signals

- Gives access to the whole device

- JTAG devices connect to form a chain

#### Abstracted from device and board complexity

No need to know what type of CPU core. or even whether the device is a CPU. FPGA, CPLD, RAM, PHY, etc.

驚かれるかもしれませんが、設計上JTAGが利用できるのに、使えるように なっていない基板が非常に多いということを、弊社は経験してきました。

まずJTAG機能にアクセスするには、少なくとも基板上のJTAG信号をシンプ ルなヘッダーに引き出す必要があります。この接続から、JTAGデバイス上の 1/0ピンにアクセスします。

そして複数のJTAGデバイスがある場合は、すべてをデイジーチェーン接続し ます。

ところで、2つのポイントがあります。

- ・まずJTAGを介して、各デバイスのピンにアクセスできるということ。 (特にデバイスがBGAや、テストポイント用に十分なスペースがない場合は 非常に重要です)

- ・そしてデバイスがIntelかARMか、FPGAかCPLDか、イーサネットデバイ スであるかにかかわらず、JTAGはすべて同じ方法で処理することです。

JTAGチェーンを適切なヘッダーに接続できれば、次にテスト容易性について考える必要があります。

ところでテスト容易性とは何でしょうか?

単純には、テストの容易性が高ければ、より多くの欠陥が検出され、製品の 品質を高めることができます。

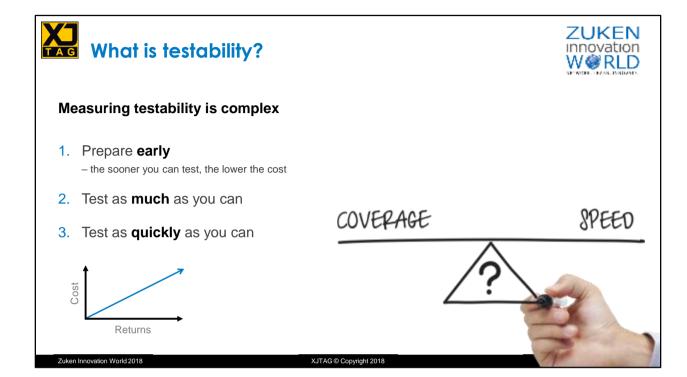

テスト容易性を評価することは複雑ですが、本質的には変わりありません。

- 最も重要なのは、事前に早期段階で準備することです。 あとから悪いテストカバレッジを改善しようとするのではなく。

- そして品質を保証するためには可能な限りテストすること。

- また、できるだけ迅速にテストして、スループットを最大化し、コストを 最小限に抑えること。

ここでカバレッジとスピードのトレードオフはビジネス上の判断ですが、それには多くの重要な要素があります:

- ・テスト手法自体のスピード

- ・テスト実行時の遅延。 例えばPCBごとの起動時間など

- ・テストに加えて、プログラミングやその検証の有無

- ・テストの実行数

- ・PCBのサイズと複雑さ

#### Testability sounds sensible

But what does it mean?

Tested for what?

前述した通り、テスト容易な設計であるほど、テストで欠陥が検出され、製品が正 しく動作することを確信できます。そしてテスト容易性とは、どれだけ簡単にテス トできるかということです。しかし、何をテストするのか?

これについて考え、何かをテストするには、想定される欠陥が無いことを確認する ということになるでしょう。ただ欠陥のリストに考えられる全ての障害が含まれる ということは、まずあり得ません。そうするとコンポーネント、またはピンが"テス トされた"とは、それはどういうことでしょうか?非常に難しい問題です。

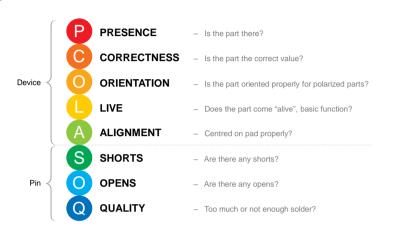

テスト容易性を評価する考え方の1つはPCOLA-SOQです。各デバイスのPresence, Correctness, Orientation, Live, Alignment、そして各ピンのオープンとショートや Qualityについての評価です。これらの中には白黒はっきり判断できるものもありま すが(Presenceはデバイスの存在有無)、それ以外はそれほどではありません。例 えば、あるピンの「ショート」をテストする場合、それは何に対してなのか? また評価項目が同じでも、JTAGテストシステムとフライングプローブでは異なるピ ンの組に対してテストをすることになります。

それゆえ適正な時間内に、一連の潜在的な障害を合理的にカバーする、適切な一連 のテストを実行することにつきます。

「注:JTAGシステムは、他のJTAGネットに対するショートをチェックします(ロ ジックまたは抵抗を介しても)。フライングプローブシステムの場合は、あるピン に近接するピンのネットとの短絡をチェックします。JTAGシステムは様々なPCBの 欠陥(PCB上のどこかのビアにトラックが近すぎてショートを起こすなど)を検出 しますが、JTAG以外のネットへのショートはチェックできません。

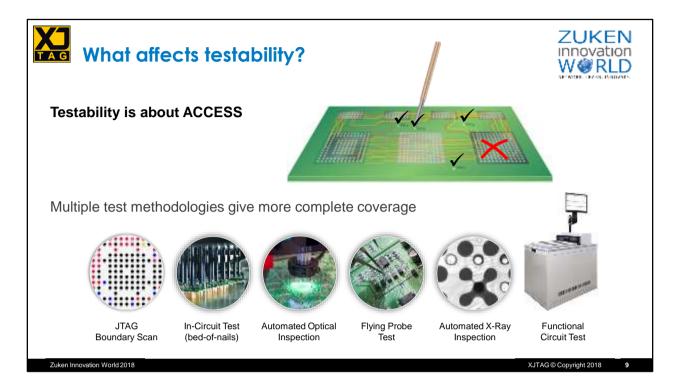

テスト容易性とは、テストするコンポーネント、ピン、ネットにアクセスで きるかどうかということです。

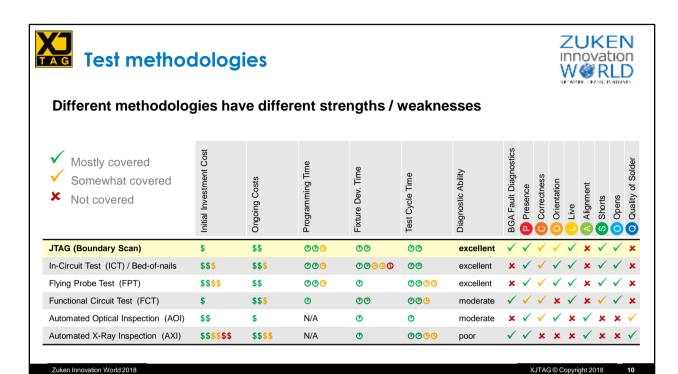

これはボードへのアクセスを増やすことで向上させることができます。 その実現手段の1つは、複数のテスト手法を利用することです。 単一の方法で全てをカバーすることはできませんので。 したがって、最良の結果を得るには、テスト手法の組み合わせが必要です。

しかし目指す結果に対して、所定の時間と予算内での実用性のトレードオフがあります。

時間とコストは、テスト容易性と併せて考慮する必要があります。 各テスト手法に、それぞれ異なる長所と短所があるからです。 そして予算内で可能な手法の組み合わせを考慮するといいでしょう。

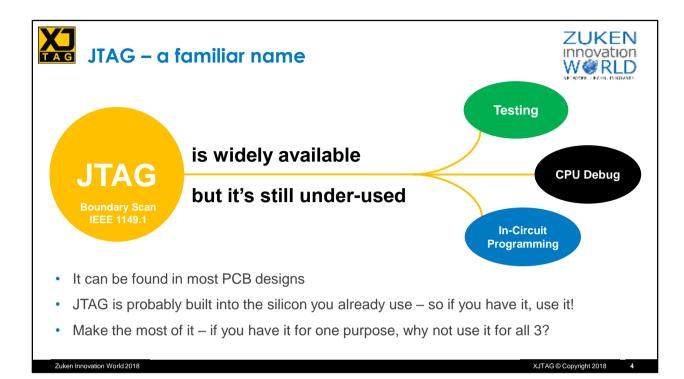

例えば、AOIを使用すると、部品が欠落しているか、はんだ品質が不良か等を確認できますが、すべてのオープンエラーを検出することはできません。BGAなどのデバイス下の実装は見えませんし、電源が供給されているかどうかもわかりません。このようなAOIのテストのカバレッジは、JTAGテストで補完できるので、これらは強力な組み合わせになり得ます。

JTAGはショートやオープンのテストに最適で、BGAのテストにベストな手法であり、 プロトタイプのデバッグだけでなく、製造時のテストツールとしても大変有効です。

またJTAGをはんだ品質や抵抗値などをテストできる別の技術(テスト手法)と組み合わせることで、テストカバレッジがさらに向上します。

フライングプローブ、プローブ治具(ネイルベッド治具)、ファンクショナルテスタ、X線等の各種テスタ、そしてそれらの組み合わせに応じて、それぞれ長所と短所、費用差があります。

## Aside: using different test methodologies

#### Different methodologies are available at different times

- ICT generally not available in the lab but JTAG is!

- X-ray may involve sending PCB to a 3<sup>rd</sup> party

また、工程ごとに適したテスト手法があります。

生産ラインでは殆どのものが利用できますが、X線などは大規模な製造工程 でしか使用できないのでしょう。

フライングプローブなどは、テスト時間の都合から大量生産にはあまり適し ていません。

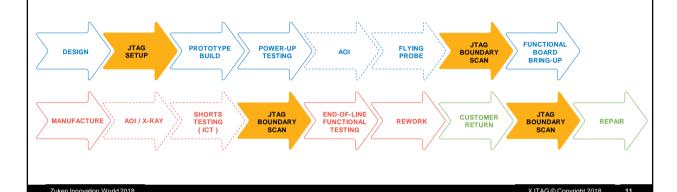

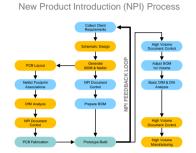

このスライド下側のフローチャート(赤と緑で表示)は、製造、テスト、修 理の典型的な流れを示します。 JTAGは、まず生産ライン上で活用され、低 コストと携帯性を活かして、修理のための診断にも使用されます。

上位の図(青色)は、多分あまり考慮されないと思いますが、R&D開発と試 作プロセスを示しています。

ここでは、プロトタイプができる前に、まず設計段階でメリットが得られま す。JTAGの設定と基板の検証を統合することで、設計上の欠陥を事前に避 けることができます。

そして最初のプロトタイプ基板ができれば、直ちにテストとプログラミング の両方にJTAGを活用して動作確認やデバッグができます。

### What affects testability?

JTAG controller

#### Testability is about ACCESS

- A point of access on a net gives you some fault detection

- Multiple points of access give you better detection and fault diagnosis

改めて、テスト容易性は回路へのアクセスのことであり、 これはボードへのアクセスを増やすことで向上させることができます。

またネットごとに複数のアクセスポイントを持たせる方法もありますが、こ れはテストカバレッジの向上に貢献するものの、複雑さが増し、テストの費 用や時間が増すことになります。

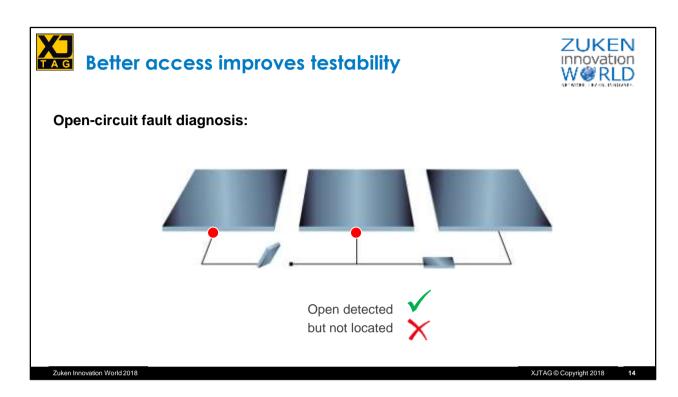

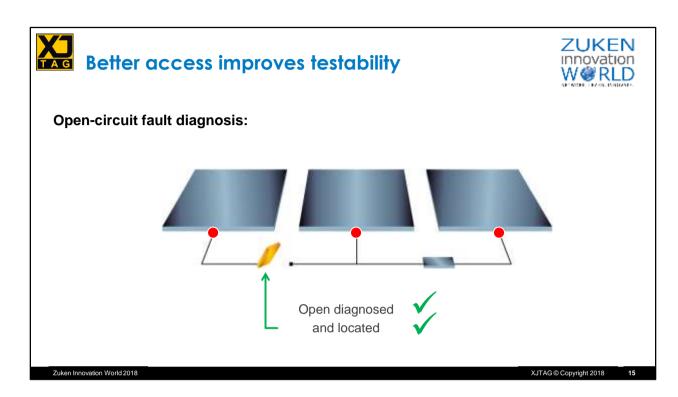

#### Better access improves testability

#### Open-circuit fault diagnosis:

Zuken Innovation World 2018

XJTAG © Copyright 2018

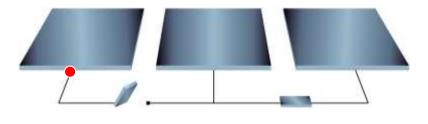

ここから3種のスライドで、シンプルなオープンサーキットを例に、テストとアクセスポイントの関係について説明します。

まず、ここで赤い点がネットへのアクセスポイントを表しています。これは 論理デバイスを介して、または他のデバイスによって制御される、直接的ま たは間接的な「アクセスポイント」です。

JTAGピンや、フライングプローブまたはテストフィクスチャ用のテストポイント、回路の他の部分から制御できるネット上のアクティブデバイス、または駆動可能なエッジコネクタピンなどです。

この図では、ネットへの単一のアクセスポイントがあります。 この場合、このネットと他のネットのショートなどをテストできますが、 オープン回路の欠陥は検出できません。

この図ではネットへのアクセスが2つあり、それらの間のオープン回路を検出することができます。

すべてのオープン回路を検出することはできませんが、一定のカバレッジが 得られます。

この図の場合は、ネットへのアクセスポイントが3つあり、ネットの位置関係から欠陥箇所を判断することができます。

すべての可能性がカバーされるわけではありませんが、問題を診断するため の詳細情報が得られます。

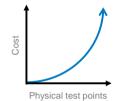

#### So the more access I have, the better?

- Yes BUT if access is by test points

- > ICT fixture complexity quickly grows

- > Flying probe test time becomes impractical

In-Circuit Test (bed-of-nails)

Flying Probe Test

多くのテストポイントを追加することは良いことですが、テストフィクス チャのコストや、テスト速度などを考慮に入れた妥協点を見出す必要があり ます。

#### So the more access I have, the better?

- Yes BUT if access is by test points

- > ICT fixture complexity quickly grows

- > Flying probe test time becomes impractical

- · Virtual test points are cheaper and faster

実装されているJTAGデバイスのピンが仮想的なテストポイントになるJTAG は、その問題に対するひとつの答えです。

先に、適正な時間内に潜在的な障害を合理的にカバーする、適切な一連のテ ストを実行することが大きな目標であることを申しましたが、プロジェクト の開発サイクルが短期間であるときは、基板のテスト容易性を確認すること を忘れがちです。

#### Typical design process - where does testability come in?

- If your design will use JTAG for bring-up, that's great!

- but make sure you don't throw away the opportunities

#### **NPI Reviews**

Is testability (and trade-off against speed) reviewed early enough in your NPI process?

#### **Design rules**

Zuken Innovation World 2018

· Sometimes you simply have to have rules.

XJTAG社では評価版に合わせて、顧客基板のテストを無償でセットアップし ていますが、テスト容易性に相当な改善が見込まれる、多くの設計に遭遇し てきました。

そのようななか、どうすれば設計者がJTAGテストの容易性についてより積極 的に関わり、ボードのリスピンを削減して、時間と費用をセーブできるよう になるかについて、我々は考察を重ねました。

#### **Design validation**

- How?

- What are the most important things to get right?

If only there were some kind of plugin that could help...!

ハードウェアが製造される前の、設計プロセス段階に、JTAGテストの容易性 に取り組むことができるソリューションがあればと考えました。 多くのボードのリスピンを削減できる設計検証ツールです。

そしてXJTAG社のJTAGテスタのIPを活用し、XJTAG DFTアシスタントを開 発し、CR-8000設計ツール用の無料プラグインツールを提供するために、 Zukenと協力しました。

ところでテストの容易性について、JTAGでは何ができるでしょうか?

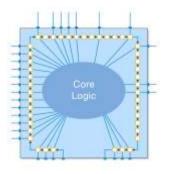

#### JTAG is unaffected by component density

· The pins of JTAG devices become test points in your circuit

#### JTAG tests non-JTAG devices

- The JTAG devices provide access to test the PCB

- Particularly useful when the PCB has BGA devices

- · Cheaper/quicker/better diagnostics than functional test

#### JTAG dramatically lowers costs

- · Simpler fixtures and test setup

- · This means it's available at a lab bench as well as in the factory

- Same tests used in production no redevelopment

Zuken Innovation World 2018

XJTAG © Copyright 2018

21

JTAGテストの容易性について説明します。

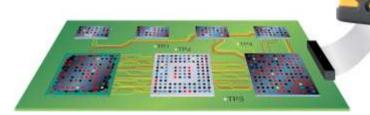

まず実装されるJTAGデバイスのピンが事実上のテストポイントとなるため、物理的なテストポイントの必要性が大幅に削減され、よりシンプルで安価なテストフィクスチャになります。

また非JTAGデバイスも、JTAGデバイスからテストされます。

- ほとんどのタイプのデバイスをJTAGデバイス経由で制御してテストまたはプログラムすることができます

- JTAGは、基板が高密度実装になってATE(自動試験装置)など他のテスト手法に 問題を引き起こすようになると、真価を発揮します

- またバウンダリスキャンソフトウェアに診断機能が組み込まれているので、問題を特定するための機能テストを独自に実装する必要はありません

以上から、JTAGバウンダリースキャンテストは、テストフィクスチャやテストのセットアップを最小限に抑えることで、コストを大幅に削減することに加えて、同じテストを生産ラインだけではなく開発室でも行えるようにして、費用対効果を最大化することに貢献します。

#### How JTAG has moved on

#### In the last 10 years...

- JTAG tools are also aimed at board designers not just production test engineers

- · Costs have fallen

- Support for non-JTAG devices is now easy

- Test scripts rather than test vectors (vectors are auto-generated)

- Code re-use both within boards and across designs

- Model libraries

- Accelerated in-circuit programming limited only by flash write speed

Zuken Innovation World 2018 XJTAG © Copyright 2018 2

ところで10年前、XJTAGが発売された当初は、まず設計エンジニアに採用され始めました。

それまでの製品は、量産検査を目的とした非常に高価で、複雑で、専門的なトレーニングを必要としたもので、またライセンスに制限があったためです。

このような従来製品対してXJTAGは、価格を大幅に引き下げて、柔軟なライセンス形式を導入し、高度なソフトウエア技術で非JTAGデバイスのテストを再利用可能なモデルにするなど複雑さから技術者を開放して、JTAGバウンダリースキャンテスタの市場にイノベーションを起こしました。

#### ZUKEN Innovation W@RLD

#### The circuit is powered during tests

Unlike AOI / X-Ray / flying probe testers

#### No firmware is used

- · Unlike functional testing

- JTAG device pins are controlled directly

#### The JTAG signals run at high speed

Typically around 10 - 30 MHz, sometimes faster

XJTAG © Copyright 2018

2

JTAGテストはターゲット電源供給状態で実行されますが、ファームウェアや ブートコードは必要ありません。

またJTAGテストをできるだけ高速に、かつ安定して行うための基本要件があります。

- ・PCBのレイアウト

- ・PCBに接続するテスト用のケーブル配線

## Test fixture cabling

#### Bad:

- Spaghetti wiring on JTAG signals

- · Poor ground connections

#### Good:

- Twisted pairs (Signal + Ground)

- · Or ribbon cables with ground between signals

- Shielded cables

#### Further reading:

www.xjtag.com/signal-integrity-in-test-fixtures/

Signal Integrity in Test Fixture

Zuken Innovation World 2018

良くない設計が多く存在することをお話ししましたが、テストフィクス チャーにも考察が必要です。

テストフィクスチャーを作る際に、PCBのループエリアを最小限に抑えるこ とが重要です。

これら信号品質に関する資料を公開していますので、ご参考ください。

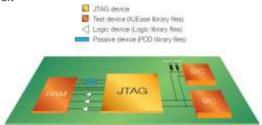

#### Testing goes beyond direct access

#### A few JTAG devices can test a multitude of non-JTAG devices on a PCB

- Testing non-JTAG devices is achieved using the JTAG device pins

- Because JTAG devices tend to be major ones (CPU, FPGA, CPLD) they have access to many peripherals

#### Access means testability

This means that from JTAG you can perform tests based on device functionality

Zuken Innovation World 2018 XJTAG © Copyright 2

改めて申し上げますが、JTAGデバイスに接続される非JTAGデバイスもテスト対象です。 そして基板上で中核的な役割を担うJTAGデバイスは、通常多くのデバイスにアクセスすることができます。

ところで、これは「デバイス機能に基づくテスト」であり、「機能テスト」 と同じではありません。

JTAGテストはデバイスへの接続を確認することが主目的であり、実速度でデバイス機能をチェックするのではないためです。

たとえば、RAMのテストでは接続をチェックしていますが、デバイス内の 個々のセルを評価するわけではありません。

#### Testing goes beyond direct access

#### **Examples of functionality-based testing**

- Use pins on the JTAG devices to write data to the non-JTAG devices on their nets, and read return data

- I<sup>2</sup>C / SPI devices

- DDR memory

- Flash

- Many others...

Zuken Innovation World 2018

XJTAG © Copyright 2018

-00

#### 簡単な例で説明します。

I2Cアクセスは、JTAGデバイスの2つのピン(データとクロック)を制御するためのものです。JTAGデバイスはバスマスタである可能性が高いため、JTAGソフトウェアでクロックエッジを生成し、適切なタイミングでデータ信号の書き込みまたは読み出しを行うことができます。

そしてJTAGデバイス上のピンへのドライブとリードで、JTAG以外のデバイスに信号を送ることで、あらゆる種類のテストを実行することができます。 例えばRAMに対するデータの読み書きを通じたテストです。RAMは高速で駆動され、定期的な間隔でリフレッシュされる必要がありますが、DRAMはJTAGテストの実行速度でテストするのに十分な期間、書き込まれた値を保持しています。

改めて、JTAGテストは、デバイスがPCBに正しく接続されていることを確認しています-オープン、ショート、誤ったコンポーネントの取り付け、などの検出です。

これはRAMやフラッシュのようなデバイスの全機能をテストしているのではなく、 またフルスピードで動作するわけでもありません(特にRAMとフラッシュの場合)。

### What faults can JTAG testing find?

P PRESENCE

C CORRECTNESS

O ORIENTATION

LIVE

A ALIGNMENT

SHORTS

OPENS

QUALITY

- · Missing or non-powered testable devices

- · Missing pull resistors

- · Shorts between nets with JTAG access

- · Shorts to power or ground

- Open-circuit between JTAG devices

- · Open-circuit between a pin on a JTAG device and a testable non-JTAG device

- · Faults in logic between JTAG devices or JTAG and testable non-JTAG devices

- Faults around coupling capacitors (using 1149.6)

- · Via functionality-based testing: huge number of additional faults

Zuken Innovation World 2018

XJTAG © Copyright 2018

27

改めてPCOLA-SOQについて – JTAGでは何ができるか?

Presence –JTAGデバイスの存在は当然確認できるし、PCB上の多くの非JTAGデバイスの存在も評価できる

Correctness - はい、コンポーネントの種類とデザインによる

Orientation - はい、コンポーネントの種類による

Live - はい

Alignment - いいえ

Shorts と Opens - かなり良い

Quality - いいえ、はんだ品質をチェックすることはできません

適正な時間内に実行できる適切なテストを見極めるために、JTAGで何ができるかを確認して、そのテスト実行を受け入れるか、別のテストと組み合わせる方が良いかどうかを判断する必要があります。

## XJTAG integrates with other test equipment

JTAGと異なる長所と短所を持つ、さまざまなテスト技術との融合事例があり ます。

XJTAGには、様々なフライングプローブ、プローブ治具(ネイルベッド治 具)、ICTマシン、ファンクショナルテスタ等で動作するオプションがあり ます。

どの技術が合うかはニーズ次第です。

JTAGをテストに使用するだけでなく、Flash、EEPROMなどの非JTAGデバイスを制御してプログラミングすることもできます。

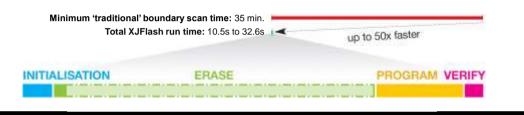

#### Programming is a pain – it takes time

- It's a pain in debug

- Uploading new firmware each time you fix a bug

- It's a pain in the factory

- Throughput matters

- Time on the production line costs money

'Traditional' JTAG is not known for its programming speed, BUT:

Accelerated programming using JTAG is as fast as it gets!

How does this work?

Zuken Innovation World 2018

XJTAG © Copyright 2018

30

プログラミングにかかる時間は、悩みの種です。

事前にプログラミングすることは、あまりお勧めではありません。 デバッグプロセス中に再プログラムする必要があるなら、その手段を提供する必要があります。

またインサーキットでのプログラミングが十分速ければ、そもそもデバイスを事前にプログラムする必要はありません。

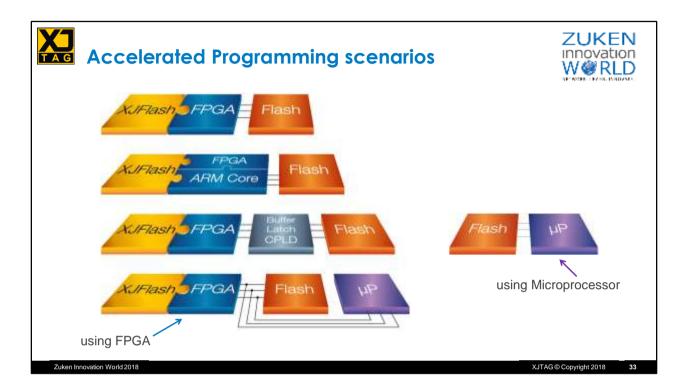

### Accelerated Programming

#### Accelerated programming can mean different things

- The PC may download some code to the JTAG controller to reduce latency/communication between them

- Better solution is to program a device on the board and use that to program the flash

- Embedded s/w program on CPU

- Image for FPGA to configure it as programmer

- Flash image can be loaded via USB/ethernet, or for an FPGA streamed over the JTAG signals

様々な高速プログラミング手法がありますが、それらの性能はすべて同じで はないことに注意が必要です。

最も速いプログラミングソリューションは、同一基板上のCPU、あるいは FPGAを使用してフラッシュに書き込むことです。

### Accelerated Programming

#### Again - some thought at design stage brings huge benefits later:

- Re-flashing during development becomes quick & easy

- Reduces production line bottlenecks caused by in-system programming

#### Maybe you have access to flash from an FPGA?

· If not, design in better access to the flash!

最高速度を得るためには、設計段階で考えなければならないことがいくつかあります。

このスライドに高速プログラミングの実例を示しました。従来のJTAG手法と比較して50倍高速に書き込みが行えています。

これはFlashメモリの速度上限に近い、非常に典型的な例です。(JTAGの速度制限を受けない)

XJFlashは当社製品の1つで、このスライドではFPGAをフラッシュプログラマとして利用することを紹介しています。

FPGAを介したプログラミングは、マイクロプロセッサ(スライドの右側に表示)を使用するより高速です。

左にサポートできる各シナリオを示します。FPGAにARMコアがあるか、またはFPGAがFLASHに直接接続されているかどうかは問題ではありません。

FPGAの通常動作では接続する必要がなくても、書き込み時にはフラッシュ デバイスの必要なすべてのラインに接続することが重要です。

たとえば、書き込み保護ピンがFPGAに接続されていることを確認します。

FPGAに接続するときは、最大幅でデータバスを接続します。

フラッシュメモリの制御線を接続します。

例えば、マイクロプロセッサとFPGAの両方をフラッシュのイネーブルピンに接続しても問題ありません。JTAGテスト時にはプロセッサは何もできないし、通常モードではFPGAは何もするように構成されません。したがって競合は起こりません。

JTAGをテストおよびプログラミングに使用する利点のいくつかについて説明 しました。

それを上手く利用するためにPCBに多少の工夫があることにも触れました。 そのことについて説明します。

#### JTAG comes with some conditions

- You have to connect it

- Signal integrity is important

- For test time

- For reliability

- For programming speed

- There may be pins which need to be accessible

- May need access to set the device into JTAG mode

#### Design and layout of the JTAG signals makes a difference

Getting it wrong can double (or worse) the time taken to test each PCB

Zuken Innovation World 2018 XJTAG © Copyright 2018

#### JTAGを正しく動作させるには、

- まずそれを接続する必要があります。

- 信号品質は重要です。一般に、これは忘れられがちですが。

- JTAGデバイスの中には、JTAGモードに入る特定の手順が必要です。

JTAGはかなり堅牢なインターフェースですが、その性能や正しい動作は回路 設計やレイアウトの影響を受けやすく、PCBの製造後に再スピンすること無 しに性能を改善することは困難です。

それゆえPCBを製造する前の準備が非常に重要です。 その最善の方法は、ツールを使ってデザインを事前検証することです。

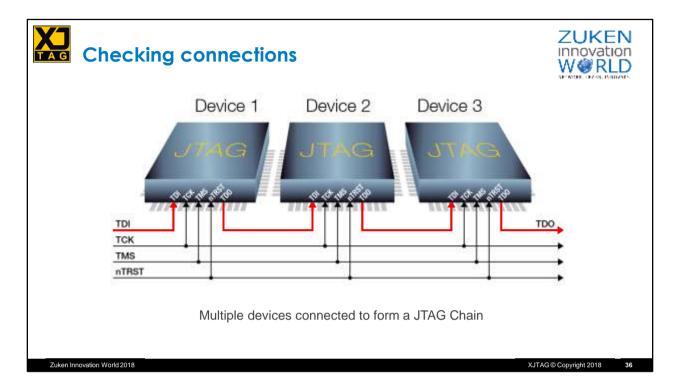

これはJTAGチェーンを形成する複数のJTAGデバイス接続です。

JTAGチェーンを形成するには、1つのデバイスのデータ出力が、次のデバイスのデータ入力に供給されて、クロックおよびその他の制御信号がすべてのデバイスに共通であることがポイントです。

またPCB上に複数のチェーンを持つこともできますし、またCPUデバッガなどの用途で、一部のデバイスを独自のチェーンにする必要もあり得ます。

基本的な接続があれば、JTAGは少なくともある程度は使用できるでしょう。 しかし、信号品質はPCBで共通の問題であり続けます。

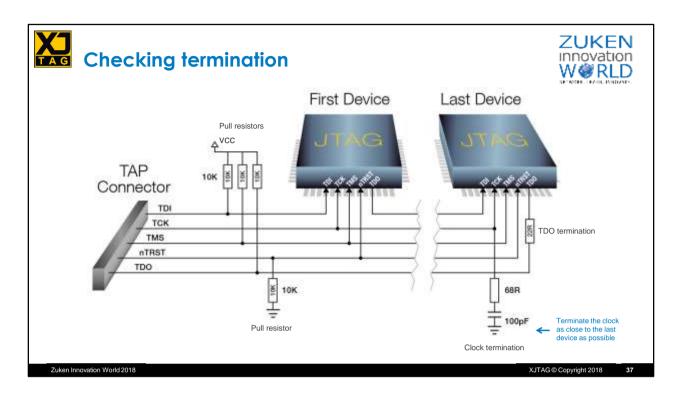

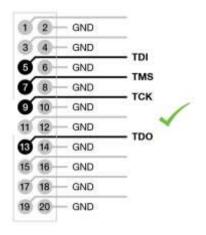

このスライドでは、JTAGを10MHzで動作させるための適切な抵抗を示しています。いくつかのプル抵抗が付加されており、クロック(TCK)信号とPCBデータ出力(TDO)信号の終端も確認できます。

良いパフォーマンスを得るためには、終端処理は本当に重要ですが、実はそうなっていないボードが多くあります。終端処理されていない場合、基板への接続ケーブル長は短くなってしまい、またテスト速度が低下します。 最悪のケースは、終端が悪いとJTAGデータにビットエラーが発生し、テスト結果のエラーやプログラミング時にデータ破損が起こる原因になります。

JTAGコントローラの中には、信号の整合性の悪さを補うための設定がありますが、設計が正しいとパフォーマンスは常に向上します!

- · Again, layout makes a huge difference

- Avoid routing TDO next to TCK

- Both on the PCB and in cabling

PCBのJTAGコネクタのピン配置を上手くすることで、信号品位の多くの問題 を避けることができます。

まず、TDOをTCKの近くに置かないことは、非常に重要です。

TDOはTCKの立ち下がりエッジで遷移するので、TDOからのクロストークに より、TCK上でグリッチが発生し、データが破損する可能性があります。

- · Again, layout makes a huge difference

- Avoid routing TDO next to TCK

- Both on the PCB and in cabling

### XJTAG Connector

ここでは若干の改善があります - TCKとTDOはケーブル内で互いに隣り合っ ていません (ピン同士は近くても)

次のポイントは、テスト対象基板とJTAGコントローラ間のグランド接続を確 実にすることです。できるだけ強固に。大抵の場合、JTAGコネクタにGND があるはずです。

これらのグランドが配線によってリンクされずに、電流リターンパスの問題 を起こすことが多々あります。

これは、どうすれば改善できるでしょう?

- Again, layout makes a huge difference

- Avoid routing TDO next to TCK

- Both on the PCB and in cabling

マイナーな改善案のひとつは、TCKとTDOを少し離れた場所に移動すること です。それらの間のGround信号で、クロストークを最小限に抑えることがで きます。

レイアウトの都合でそれができないなら、TCKをGNDの近くに配置するか、 JTAG動作中に変更しないピン(例えばtest reset (nTRST) ) の近くに配置 します。

- · Again, layout makes a huge difference

- Avoid routing TDO next to TCK

- Both on the PCB and in cabling

- · Use multiple Ground connections in the cable

- Interleave them if you can

#### XJTAG Connector

このピン配置は、より優れた解決策です。

アクティブな信号をグランド(GND)ピンとインターリーブすることで、回 路図設計の段階で信号品質の問題を最小限に抑えることができます。 この場合、偶数番目のピンはすべてグランドです。つまり、各アクティブ信 号間にグランドが存在します。

ところで弊社では、顧客の様々な種類の問題を経験することで得た多くのノ ウハウをドキュメントにまとめています。

- Again, layout makes a huge difference

- Avoid routing TDO next to TCK

- Both on the PCB and in cabling

- Use multiple Ground connections in the cable

- Interleave them if you can

- Don't forget JTAG mode pins

- Route to header or have some way to set them

- Keep track lengths/buffer delays as similar as possible

- Particularly for TMS and TCK

Zuken Innovation World 2018

https://www.fuji-setsu.co.jp/products/XJTAG/JTAG.html#DFT

このDFTガイドライン(日本語版)の冊子を、ZUKEN Innovation Worldの XJTAG社展示スペースでお配りしています。

PDF版をXJTAGのウェブサイトからダウンロードすることもできます。

https://www.fuji-setsu.co.jp/products/XJTAG/JTAG.html#DFT

JTAGバウンダリースキャンテストについて

https://www.fuji-setsu.co.jp/products/XJTAG/JTAG.html

### XJTAG DFT Assistant for Zuken

#### Free Plugin

- · Helps reduce board re-spins

- Easy to use

- · Fully integrated into CR-8000 Design Gateway

#### Download from:

www.xjtag.com/zuken

動画デモ https://www.fuji-setsu.co.jp/demo/XJTAGdftZUKEN.wmv

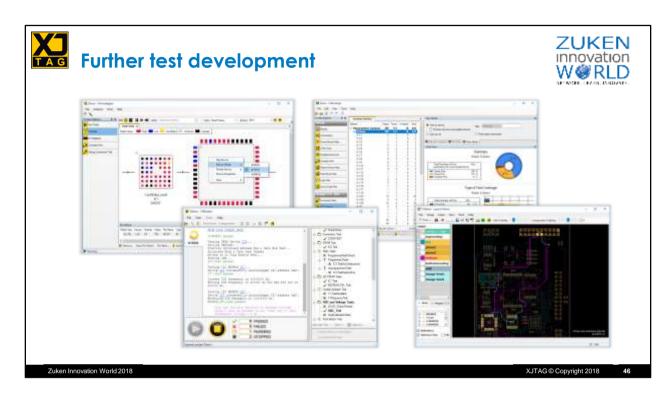

ここからZuken用のXJTAGプラグインで、回路設計段階でテスト容易化を自 動でできることについて説明します。

#### 動画デモ

https://www.fuji-setsu.co.jp/demo/XJTAGdftZUKEN.wmv

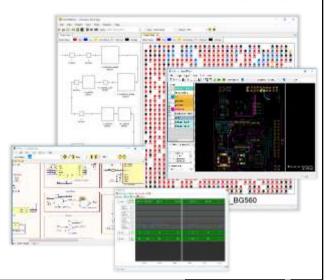

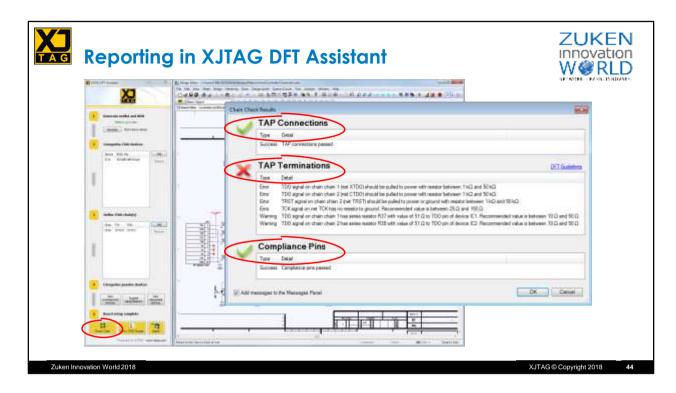

XJTAG DFT Assistant は、JTAG信号の接続と終端をチェックし、問題個所をレポートします。

この例では、チェーンが正しく接続されていることがわかります。

しかしプル抵抗が欠落しており、また終端抵抗に仕様外のものがあることを 報告しています。

また、コンプライアンスピンへの適切なアクセスをチェックします。これらは、JTAGテストを実行するために正しい状態(または制御可能)である必要があるJTAGデバイス上のピンです。

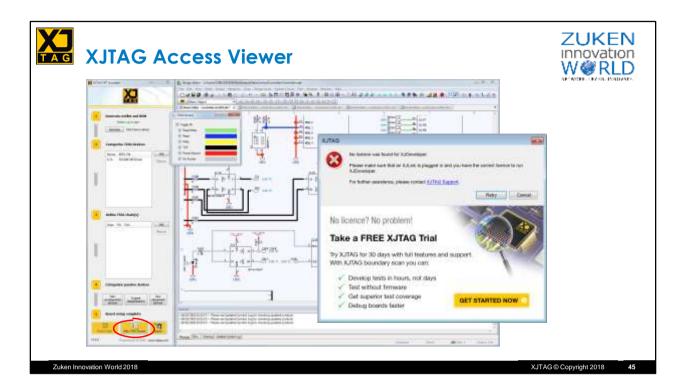

JTAG接続を確認できたら、XJTAG Access Viewerを使用します。

これは回路図上でJTAGアクセスの程度が色分け表示され、現状テストできない箇所をハイライトして評価することができます。そしてデザインを変更して、再度このビューを生成して、テストアクセスがどのように改善されるかを確認します。

この作業の繰り返しで、JTAGチェーン接続上のミスを排除して、テストカバレッジを改善して、再スピンの可能性を削減して、製品を納期通りに予算内でリリースすることが期待できるようになります。

更に、ここで得られた成果物は、バウンダリースキャンテストのプロジェクトに利用することができます。

DFT Assistant に入力したデータはXJTAGプロジェクトに変換され、テスト実行やテスト容易性レポートに利用されます。

JTAGで多くの時間とコストを削減できることを紹介してきました。

### Saving time and money

#### Thinking about JTAG at the design stage...

- Get the JTAG chain(s) right use a plugin to verify your board design

- · Consider signal integrity for JTAG traces

- Consider improving access to flash devices

- Use DFT analysis from your JTAG software to improve testability

#### まとめ

- JTAGチェーンを正しく XJTAG DFT Assistantで設計を確認してくださ い。これは無償ツールでダウンロードできます。

- JTAG信号品質を考慮する

- フラッシュデバイスへのアクセスを改善することを検討する

- JTAGソフトウェアのDFT解析を使用してテスト容易性を更に改善する

## Saving time and money

#### Thinking about JTAG at the design stage...

...brings benefits sooner than you would think:

- Use JTAG to test your prototypes

- Re-use those tests on the production line

- · Benefit from the test coverage that JTAG gives you

- Use accelerated JTAG solutions for in-system programming

- both for debug and for production

設計段階でJTAGを考慮する... ...より早く利益をもたらすために:

- JTAGを使用してプロトタイプをテストできる

- テストを生産ラインで再利用する

- JTAGバウンダリースキャンテストでカバレッジを補完することで、多く のテストフィクスチャを削減できる

- デバッグと量産の両方にJTAGによる高速Flashプログラミングを検討する

### Saving time and money

**Use JTAG more**

#### Make use of the **FREE STUFF!**

- Zuken CR-8000 Plugin

- **DFT Guidelines**

- Signal Integrity article

PCBが製造される前の、早期段階からJTAGを検討することで、プロトタイプ ができれば直ぐにテスト、プログラミング、デバッグを開始できます。

そしてXJTAG DFTアシスタントをダウンロードすれば、テストの容易性の評 価は無料で行えます。

DFTガイドラインのダウンロードもお忘れなく。

https://www.xjtag.com/ja/about-jtag/design-for-test-guidelines/

是非、展示コーナにもいらしてください。

DFTガイドライン(日本語版)の冊子をお配りしています。

富士設備工業株式会社電子機器事業部 www.fuji-setsu.co.jp