# Model-Driven Verification and Validation

## モデル駆動による V&V について

Presented at: Safe & Secure Systems & Software Symposium June, 2010

> By Mark R. Blackburn, Ph.D.

T-VEC Technologies, Inc.

\*Safe & Secure Systems & Software Symposium June, 2010 http://www.azimuth-corp.com/conference/S52010/

(Air Force Research Labs (AFRL), National Science Foundation (NSF), Defense Research Project Agency (DARPA), NASA の主要研究者が参加するカンファレンス)

## エンジニアリングの基本的なアプローチは1960年から変わっていない

Making DARPA META Goals Come True: How do we Revolutionize Verification and Validation for Complex Systems?

Dr. Kirstie Bellman, Aerospace Integration Science Center (AISC) The Aerospace Corporation

( http://www.azimuth-

corp.com/conference/S52010/papers/presentations/Day\_3/Making%20DARPA%20META%20Goals%20Come%20True%20-%20How%20do%20we%20Revolutionize%20Verification%20and%20Validation%20for%20Complex%20Systems%20[Bellman].pdf )

発表者であるMark R Blackburnは、25年間セーフティクリティカルなシステムの開発に関わってきた(FAA DO-178A、DO-178B 認証、FDA関連システムへの取り組みなど)

V&V 作業の多〈を自動化支援する仕組みを考案し創出

形式手法による定理証明であり副産物としてテストベクタを生成できる

セーフティクリティカル、ミッションクリティカル、商用システムに活用されてきているが、まだ広〈知られるに至っていない

META プログラムで紹介された課題克服に活用できる特徴を紹介する

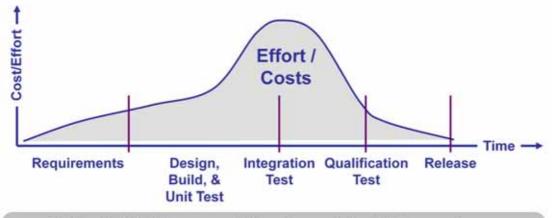

2009 - META Program: Failure to update 1960s- systems engineering process significantly increases cost and schedule 1960年代からSWエンジニアリングプロセスは変わっていない

Copyright © 2010, T-VEC Technologies, Inc.

2

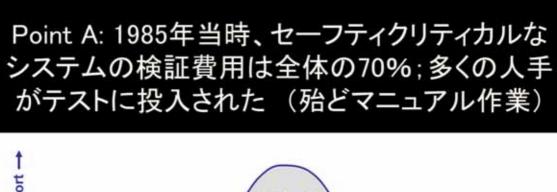

- 1. 1985年にFAAの認証を取得した時の例

- 2. このセーフティクリティカルなシステムの70%の工数は検証作業

- 3. 検証のエビデンスを得るためにプロジェクト後期に多くの人が投入される

- 4. 殆どのテストはマニュアル(人手に頼った作業)

目的はより進んだエンジニアリングツールの応用。IC(集積回路)開発で行われているのと同様の、より厳密で建設的なアプローチをSWエンジニアリングプロセスに持ち込むこと

Image credit: DARPA META program *APPROVED FOR PUBLIC RELEASE. DISTRIBUTION UNLIMITED*

### **V&V** cost and Certification

For FAA compliant DO-178B Level A software, the industry usually spends 7 times as much on verification (reviews, analysis, test). So that's about 12% for development and 88% for verification.Level B reduces the verification cost by approximately 15%. The mix is then 25% development, 75% verification.

Randall Fulton FAA Designated Engineering Representative

# Joseph Sifakis (one of the 2007 ACM A.M. Turing Award winners) はモデリングとソフトウエアシステム の検証に付いて以下のように言及している

- 複雑なシステムを忠実に数学的モデルにすることは非常にチャレンジングである

- ► HWなら数学的モデルにすることは比較的容易であり多くの 成果が得られている

- ➤ SW では厄介。どのように実装されるかによる。しかし多くの複雑なSWを検証できる

- ▶ しかしHW上で実行されるSWで構成されるシステムの場合、検証のために忠実な数学的モデルを構築する方法を知らない

Quotes from Talking Model-Checking Technology by Leah Hoffman (A conversation with Joseph Sifakis the 2007 ACM A.M. Turing Award winners.)

4

## ここでキーポイントは、

- 1. ハードウエアを数学的モデル化することは比較的容易

- 2. ソフトウエアでは難しくなる。どのように記述されているかが問題になる

- ・ 一般に仕様上のエラー削減は、実装に対するそれに比較してインパクトが大きい[Nancy Leveson].

- T-VECは仕様・設計モデルを形式手法のよって定理証明し、テストベクタを生成できる。それはリニア、ノンリニアをサポートし、フロートやダブルなどあらゆるデータ型に対応するので、実HWシステムレベルで仕様・設計と実装の一致性検証に活用できる。

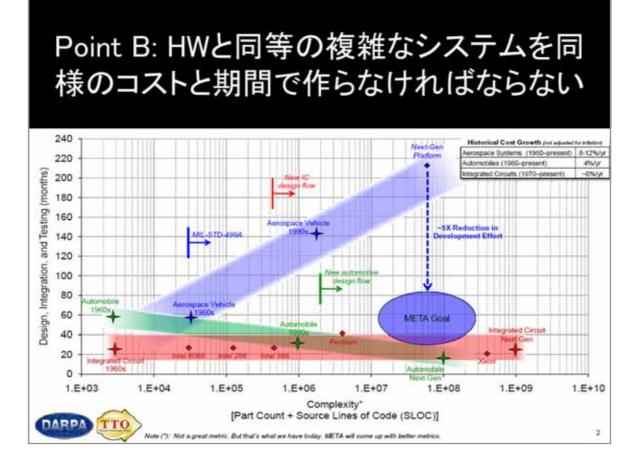

# Call to action: ソフトウエアシステムとハードウエア(IC)の違いに取組む必要がある

- 1. ハードウエアとソフトウエアの多くの違いについて論ずる前に

- 2. 基本的な違いのひとつを見てみたい。それはソフトウエアの振舞いの中で、フローティングポイント型の変数に対するノンリニアな関係・コンストレインツがHWとの違い

## 3つの重要課題

- ソフトウェアの実装方法に依存する

- ▶ モデルは実装にマップされる必要がある

- 検証エンジンは強力でなければならない

- ▶ あらゆるタイプのモデル構造部品、ノンリニアでさえ扱えないといけない

- モデリングは簡単でなければならない

- 形式手法や定理証明を知らないでも使えること

Copyright © 2010, T-VEC Technologies, Inc.

6

## このプレゼンで紹介する3セクションには2つの横断するテーマがある

- ソフトウエアの記述方法によって自動検証への影響があること

- 実装にマップされるモデルの構造部品の全てのタイプを十分に扱えないような検証エンジンでは使い物にならないこと

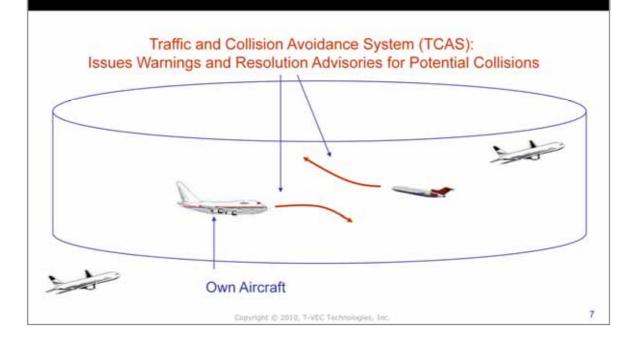

# Key Point #1 - 1988 - 航空機のトラッキングシステム のノンリニアなファンクション、コンストレインツのモデ ルベース検証の課題に取組んだ

- 1. 1988年に検証に対する基本的かつ費用の掛かる問題に取組む機会を得た

- 2. 体系的に支援できる手法とツールを決定する機会を与えられた

- 1. このプロジェクトでFAAと密接にコンタクト。要求仕様ベースのテストが一つの目標であった

- 2. 上流の要求仕様、実装から派生される要件、安全性のための要件など、全てに対して同様に従来からのVモデルを採用した

- 3. そしてソフトウエアシステムの全てのスレッド(タスク)に同じプロセスを採用

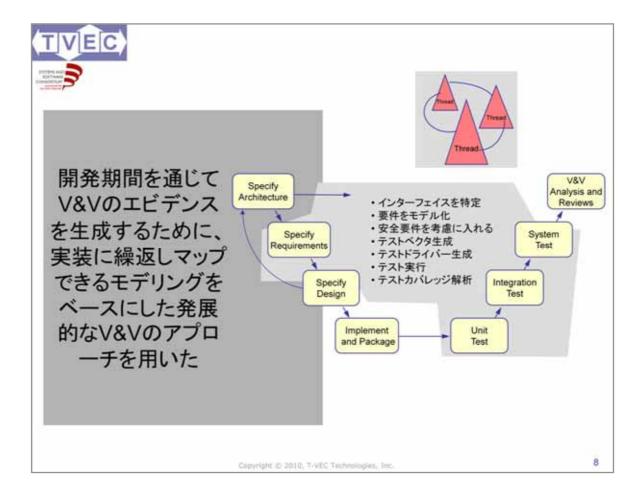

- 4. 開発期間を通じて検証のエビデンスを生成することを目標として

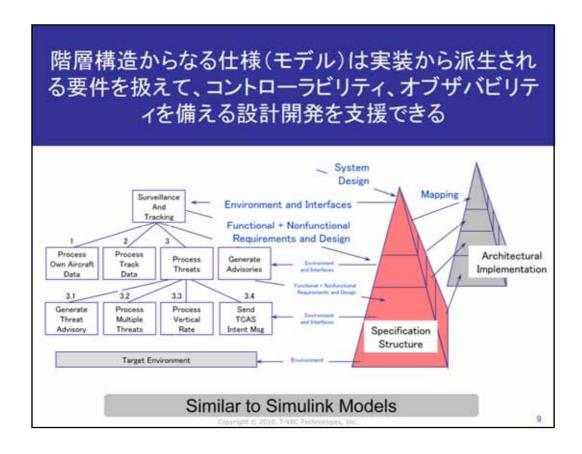

- 1. 実装にマップできる階層的な仕様(モデル)を創出

- 2. インターフェイスが次の要素をサポートすることを意識した。

- コントローラブル·制御可能(入力と状態の設定)、オブザバビリティ·可観測性(出力を得る)

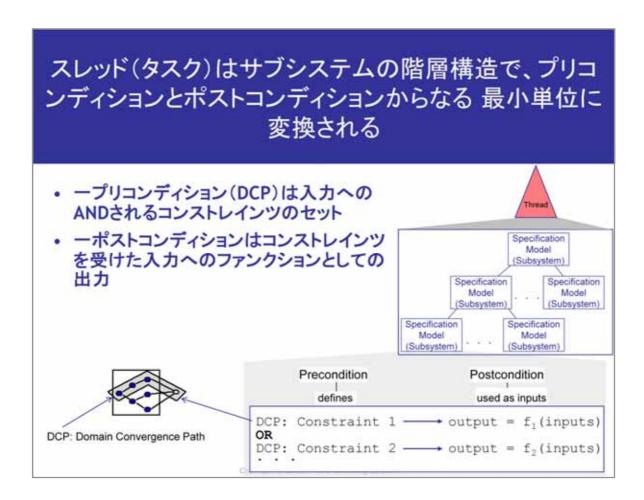

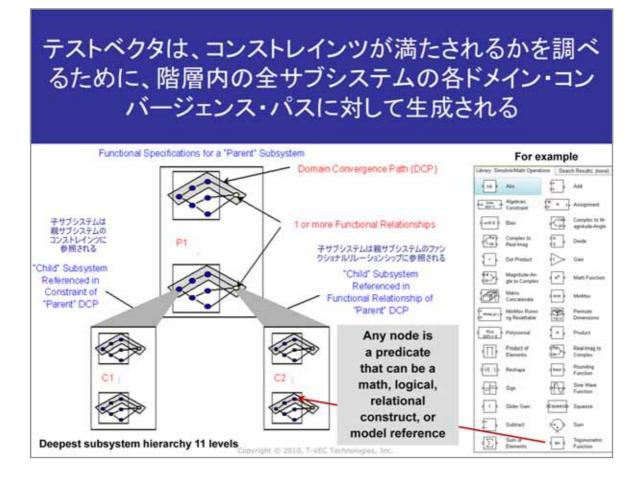

- 1. 全てのスレッド内の全サブシステムはDCP( Domain Convergence Path )というローレベルの形式に変換

- 2. DCPは本質的に、プリコンディション(入力とコンストレインツのセット)とポストコンディションとして表現されるファンクショナルリレーションシップ

- 1. サブシステムの階層構造からなるシステムを形式手法で定理証明する仕組みの説明

- 2. 各サブシステムは1つ以上のDCPを持ち、その各ノード(コンストレインツあるいはファンクション)は本質的に述部として、他のサブシステムへのリファレンスとなる。

- 3. それゆえファンクションはコンストレインツとして、上流レベルのプリコンディションの一部となる

- 4.これら述部は標準的な数学、数理論理学、プログラム言語の論理オペレータなどで構成されるが、 Simulinkのモデルライブラリ部品もサポートする

- インテグレータ・積分器

- N次のインターポレーションテーブル

- 5. T-VECはコンストレインツ(DCP)をベースにしてサブドメインの入力領域からテストデータを選択・抽出

- 6.DCPはMCDCテストカバレッジをサポートするために、相当するプログラムのパスコンディションにマップされる

- \*親側のコンストレインツを受ける変数の入力レンジは、下流のサブシステムのコンストレインツも受ける。そこで得られる入力領域内で期待値が取れるかを検査するテストベクタ生成を行い、サブドメインのDCPがシステム内で成立することを証明する(T-VECによる形式手法、定理証明)

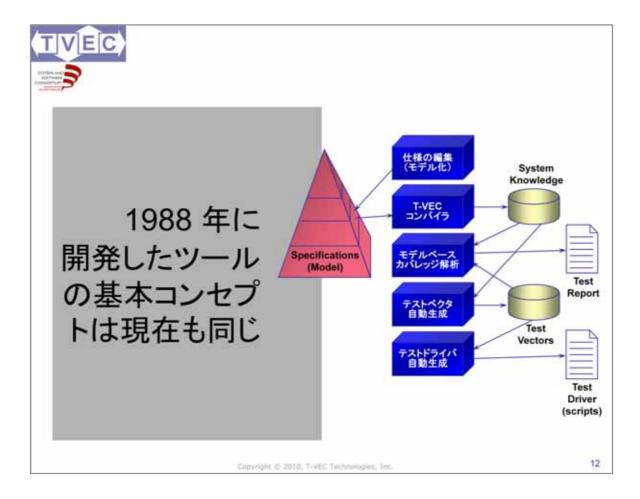

- 1. 仕様記述のエディタ機能を拡張したことを除いて、ツールの基本コンセプトは現在のツールと同じ

- 2. 階層からなる仕様はローレベル(DCP)に変換されてSystem Knowledgeとして保存される

- 3. このSystem Knowledgeはテストベクタ生成のために使用される

- 4. モデルベースカバレッジ解析は、ずべてのDCPがテストベクタを持つことを解析する別のツール

- テストベクタが持てない場合、モデル上に問題があるということ

- この手の問題を、この後簡単に紹介する

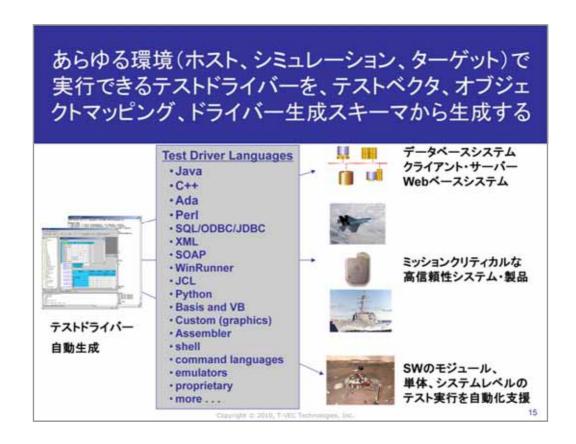

- 5. 生成されたテストベクタを用いてテストドライバーを生成する機能がある

Page 12 12

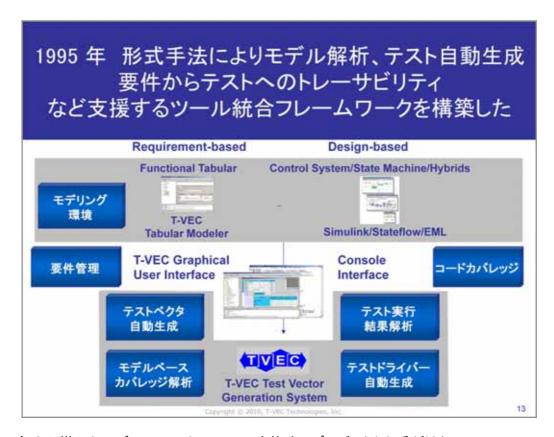

- 1. 1995年から様々なモデルツールをT-VECに変換するプロジェクトを手がけた

- 2. Consortium Requirements Engineering Method (CoRE)をサポートするSCR

- 3. CoREの基であるSoftware Cost Reduction MethodをサポートするSCRツールは Naval Research Laboratory (米·海軍研究所) で開発された

- 4. F16向けにMATRIXx にも対応

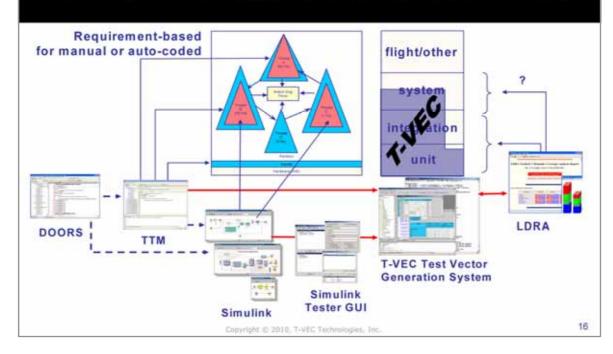

- 5. またDOORSといった要件管理ツールとの統合、LDRA社のコードレベルのテスト実行・カバレッジ解析機能との統合も、顧客の要求に合わせて行ってきた。

- 6. T-VECの自動テストベクタ生成システムは、モデル解析、テストベクタ生成、要件からテストカバレッジに至る解析、テストドライバー生成を行えるので、検証・テストに於ける人手に頼って間違いの基になりやすい作業の多くを自動化できる。そして開発ライフサイクルに一貫したテストを支援して、市場投入までの時間を削減し、開発とメンテナンスのコストを軽減し、製品品質を向上させることに貢献する形式手法・定理証明のツール。

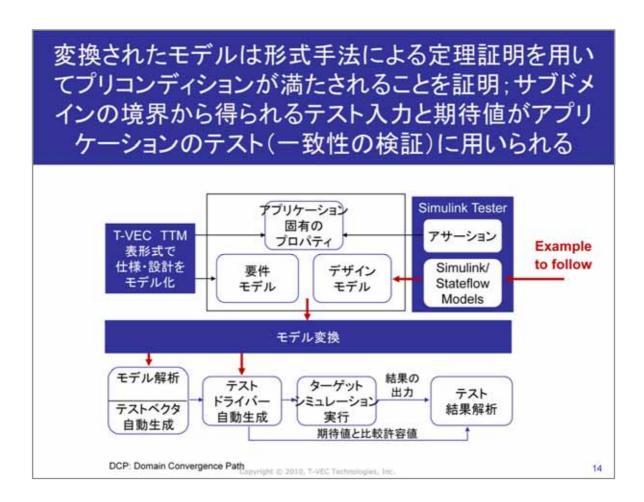

- 1. モデルは要件、デザイン、アプリケーションの特性・プロパティ(安全特性など)を描写できる

- 2. それらはローレベルの形式(DCP)に変換される

- 3. モデル解析は形式手法による定理証明(事前条件を満たす入力の有無を証明する)

- 4. ベクタ生成機能がサブドメイン境界の入力値に対する期待値を計算

- 5. テストドライバー生成機能を用いてテストベクタは、あらゆる環境下で実行して結果を得るためのテストドライバーに変換

- 6. テストベクタ内の期待値をテスト結果として得られる実出力値と比較

様々な言語環境、実行環境に合わせたテストドライバー生成に活用できるテンプレート(スキーマ)を提供

# Key Point #2 -ツールチェインが必要: ーつで全てに対処できるツールは無く 個々のツールの際立った特徴を活かす必要がある

- 1. テキストベースで管理される要件からテストに至るトレーサビリティを支援できる開発ライフサイクル に一貫したツールチェインが求められる

- 2. ライフサイクルの殆どの部分をサポートできる特別なツールが必要

- 3. コード生成が出来ることで制御系システムでSimulinkはポピュラーとなっているが全システム内の30%を作っているにすぎない

- 4. TTMはSimulink以上にシステムの他の部分の機能性のモデル化に活用される

- 5. 単体テスト、HWとSWの統合テスト、システムテストに活用できる

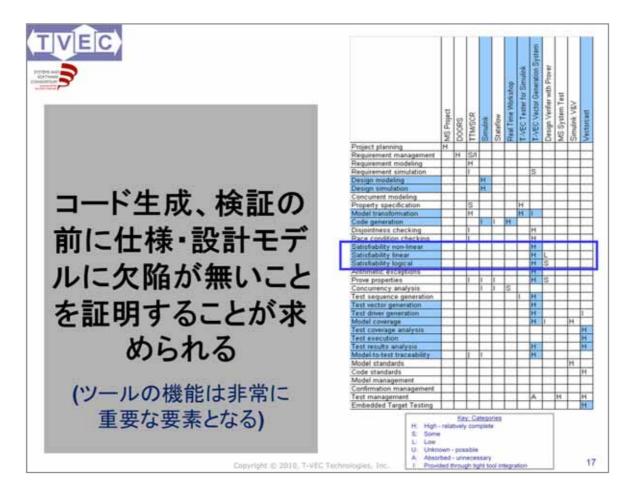

- 1. ある企業からツールチェインの有効性に関しての調査依頼を受けた

- 2. モデル解析とテスト生成能力についての興味

- 3. モデル上のロジカル、リニア、ノンリニアなコンストレインツの解析能力に関して調査した

- 4. モデルが変換されてコードとして生成されるのなら、モデルに欠陥が無いことは重要

Page 17 17

# 単純なノンリニア操作(フローティングポイントデータ) 上の欠陥を持たせた Simulink モデルのサンプル 「Notice for the first for th

- 1. 欠陥を含むモデルを作った

- リニアなコンストレインツを満たさないものと、

- ノンリニアなコンストレインツを満たさないもの

- 2. 赤で囲まれた / ンリニアなコンストレインツは下層サブシステム内の Gain ブロック (増幅器) に関係する

- シンプルなノンリニアな関係であるが

- 3. 次のスライドで詳細

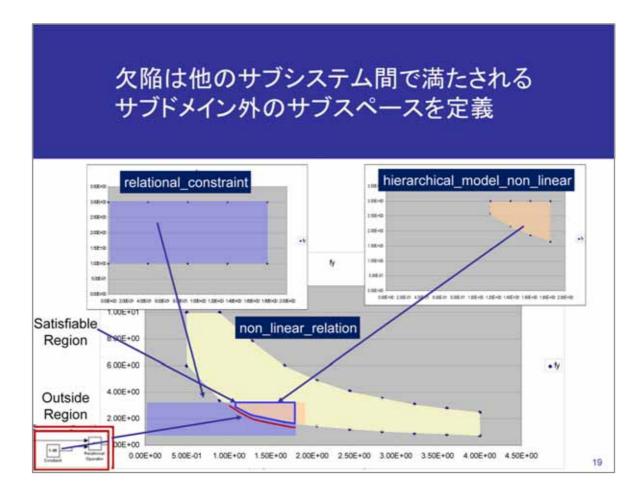

- 1. 3つのサブシステムごとで制限された領域(constrained space)

- 2. 小さな赤色の線はリレーショナルオペレータのコンストレインツがオーバラップする領域から外にあることを示している

- 3. 結果、全てのコンストレインツを満たす入力領域が存在しないことがわかる

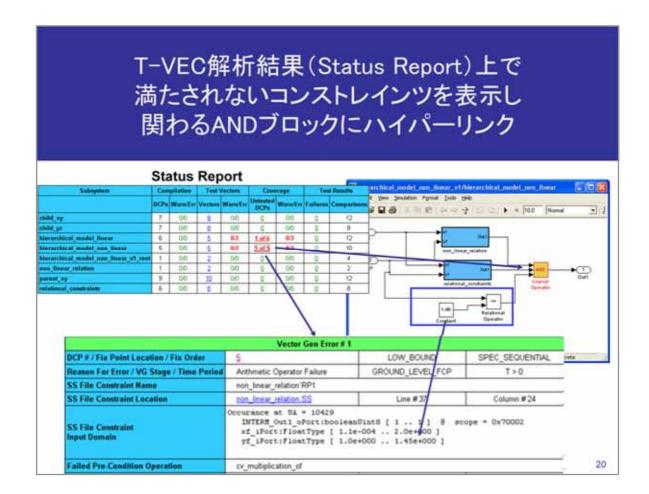

- 1. T-VECのステータスレポート上に、テストベクタを生成できないDCPが有る事が表示(リニアとノンリニアの両方)

- 2. それらはモデルの問題箇所にハイパーリンクできる

- 3. この例ではANDを満たせないということ

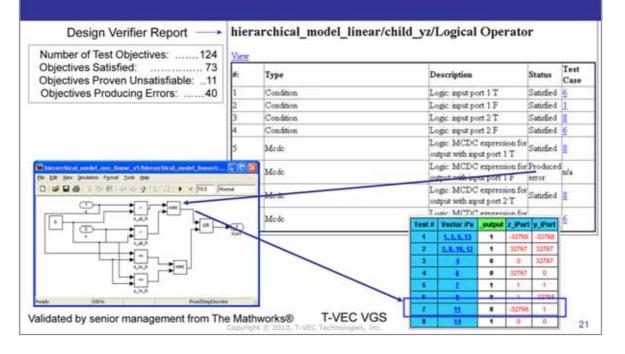

# Mathworks 社 Design Verifier (DV) では 複数の満たされる対象にテストが生成できなかった (T-VECではテストベクタを生成)

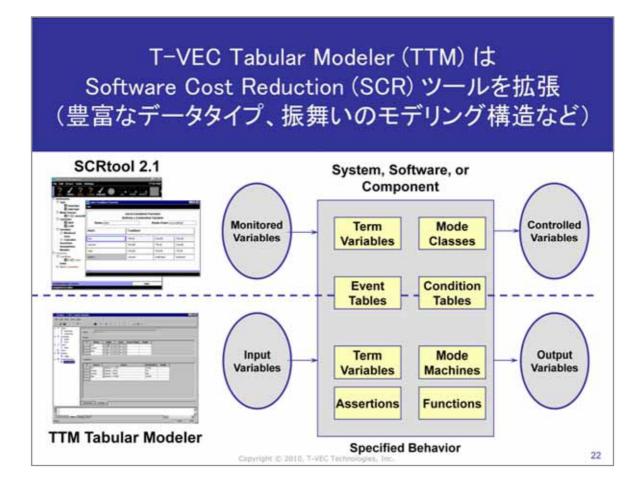

- 1. TTMはSCRツール・手法を拡張したもの

- 2. SCR は、the Naval Research Lab back about 1980; also referred to as Parnas tables after Professor David Parnas 氏により開発された

- 3. オリジナルでは インテジャ、ブーリアン、フロートなど(scalar data type)のみであったが、構造体や配列もサポートできるようにした

- 4. TTM added:

- 要件管理

- 構造体、配列、ストリング

- モデルリファレンス

- 要件へのトレーサビリティ

- 追加機能(In, log2, log, ceil, floor, round, truncate)

- パラメータ化された関数

- アサーション

- インライン化

## モデルリファレンスにより継承、オーバライド、 インターフェイスの振舞いからの分離を可能にし より良いモデルの管理や再利用を支援する Tracking & Avoidance Behavior Avoidance **Altitude Processing** Vertical Tracker Processing Interface X X Altitude Vertical **Avoidance Processing** Tracker **Processing** インターフェイスを規定するTTMモデルを包含し、 個別のモデル内にコンポーネントの振舞いを規定 23 Copyright © 2010, T-VEC Tech

- 1. TTMへの拡張 モデルリファレンス、継承、オーバライドなど

- 2. モデルリファレンスによってインターフェイスを振舞いから分離し、一つのインターフェイスを定義して参照できるようになる

- 3. モデル上の変数と実装上のインターフェイスのためのオブジェクトマッピング

- 4. モデルの振舞いはインターフェイスのモデルを包含し、振舞いの組合せをサポートする

- 5. これによりモデルはシステムのアーキテクチャを正確に描写することになる

- 6. 統合テストをサポートするためのテストがモデルから生成できる

# T-VEC Tabular Modeler (TTM) と テストベクタ生成システムの、 ドメインスペシフィックモデリングツールとの統合

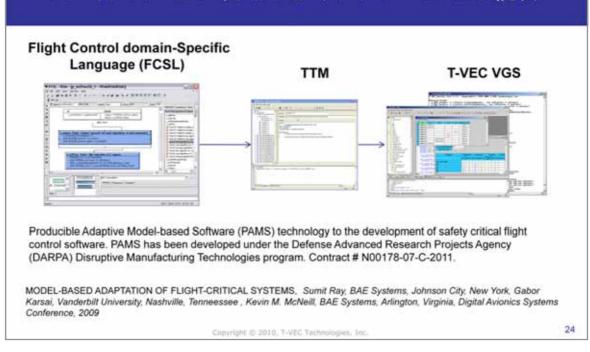

- 1. BAEシステム社、Vanderbilt University とドメインスペシフィックモデリング言語の活用について協力した

- 2. TTMモデル言語はT-VEC形式より抽象度が高い

- 3. それゆえドメインスペシフィックモデリング言語をモデル解析、テストベクタ生成に適した形式に変換することが容易

- 4. SimulinkもDSMLであるが、大きくて複雑な言語(ドメインが広いので)

# Key Point #3 -飛躍的なコスト・工数の削減には根本的な改革が望まれる | EEEE MetroCon 2002 | Software / Telecom Track | First Moves Define Results | First Moves Define Results | Tools | Software | Telecom Track | Tools | Too

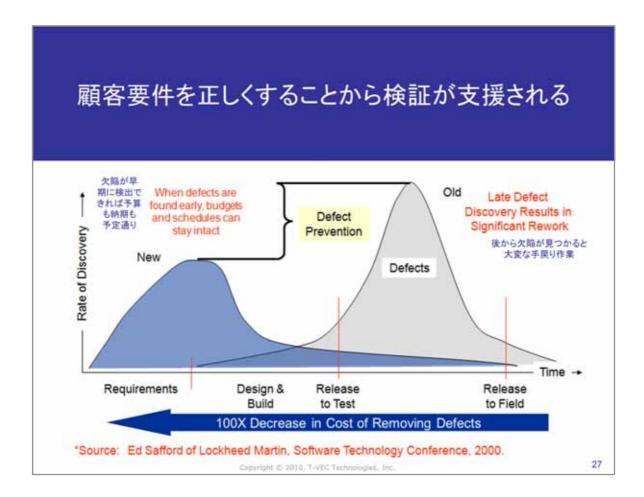

- 1. Lockheed Martin 社の許可を得た図

- 2. ここで肝心なことは開発費用の70%は早期段階で決定されてしまうということ

- 3. なぜソフトウエアシステムの検証費用が高価になるのか? IC開発者のように体系的で自動化されるV&Vを採用できないと、自らマニュアルで検証作業にあたることになり高価になってしまうということ。

- 4. 複雑なセーフティクリティカルシステムでは70%以上にもなっている

### 形式手法の活用で早期段階からインターフェイスを明 確にした要件モデリングで要件上の欠陥の検出・削除 を支援し、実装前にテストを提供できる 要件開発担当者 デザイン/実装担当者 要求仕様 System (様々な形式で供給される) · SRS · Function List · Change Request · API エンジニア (モデリング担当者 Component Interfaces Test Results Test モデル Vectors テストペクタ 自動生成 テストドライバー 自動生成 インターフェイス 振舞い Data Types Variables + Conditions Test Events Drivers State machines Constants Functions **Test Driver** mapping schema エンジニア (自動化担当) --- Time

- 1. Lockheed Martin 社の実績

- 2. 図の見方は左から右への時間経過

- 3. 要件開発時からモデリングを採用し、要件上の問題は顧客と確認することなどを介して正すことができた。

- いかに早期の要件検証が行えるかの実績

- 4. 早期のインターフェイス解析を併合したことで、システムインターフェイスの観点から要件や派生要件をモデルに仕様化できる。

- 5. そして形式手法により定理証明、早期のテストベクタとテストドライバー生成を可能にし、デザイン 担当者や実装担当者は早期段階から継続的にテストが行えるようになった

- 1. Ed Safford of Lockheed Martin at the STC conference just before the JSF award からの図

- 2. モデリングにより欠陥を封じ込めることと、モデリングのプロセスで欠陥を未然に防ぐことを証明した

- 3. 多くの欠陥は形式手法による定理証明によって早期に認識され、手戻り作業を削減できた

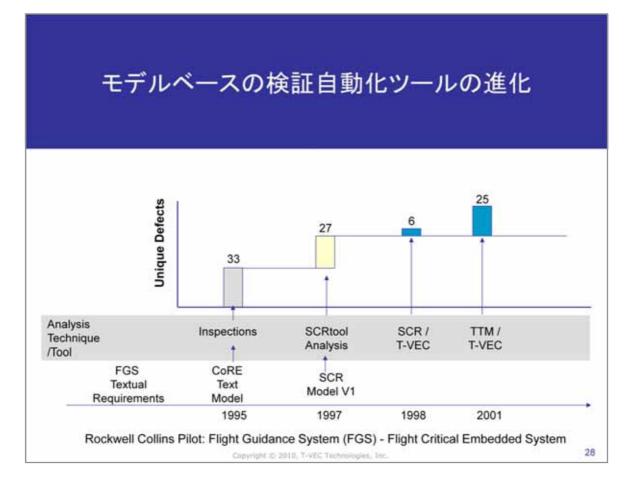

- 1. Rockwell Collins on a Flight Guidance Mode System 社でのFagan inspection の実績

- 2. 当初はテキストドキュメントをCoREツール(テキストベースのSCRへ)

- 3. SCRツールがリリースされ追加の欠陥を検出し、それが進化してT-VECの形式手法(定理証明+ テストベクタ生成)と統合されることで更なる欠陥を検出できるようになった

Fagan inspection refers to a structured process of trying to find defects in development documents such as programming code, specifications, designs and others during various phases of the software development process. ... http://en.wikipedia.org/wiki/Fagan inspection

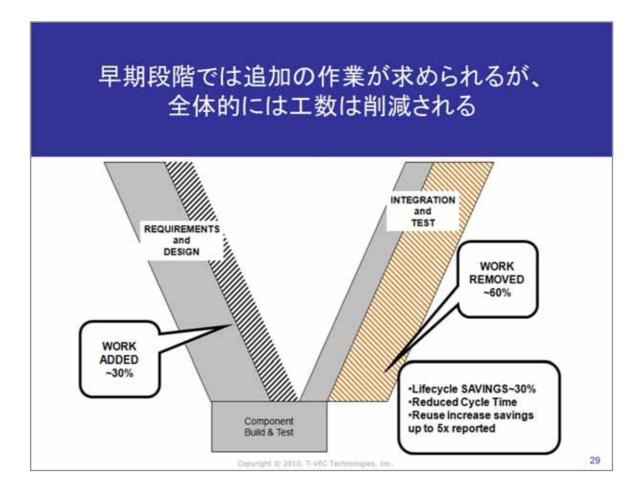

- 1. Lockheed Martin, Rockwell, NIST などによりこれらの実践的な事例が公開されているが、多くの企業は公開したがらない(C-5の事例のように既存製品との比較が出ることが躊躇されるので)

- 2.この図は上述企業とは別の会社で、開発ライフサイクルへの影響を考察するために作成された

- モデリングにより上流工程に追加の工数が求められるが、下流工程を削減した

- モデルの再利用により5倍の効率になることは重要なポイント(既存モデルを再利用して拡張することができる)

- モデルの機能は製品ごとで共通なので、運用上の再利用(共通ツールに対する理解・ 経験)なども効率化できる

## **Organizational Best Practices**

インターフェイスドリブンなモデリングは開発しながら適応させることに飛躍的な効果が認められた。理想的にはテストエンジニア(モデラー)が開発者と共にインターフェイスを安定させて、要件を精練し、イテレーティブに反復して開発・テストできるようなモデルを作る。テストエンジニアはモデルを介して製品の要件(通常殆ど不完全なままの)を精練する、それは数百・数千行ものテストスクリプトを書〈代わりに。そして形式手法を用いて仕様・設計モデルを定理証明し、テストベクタ(入力と期待値)・テストドライバーを自動生成。イテレーティブに反復される開発の中、コンポーネントの振舞い、インターフェイス、要件などが変更される場合、モデルは修正され、テストケースとドライバーが再生成され、再実行できる。このツールの特筆すべき優位性は、テストのプロセスが通常の開発と同時に行えること。Lockheed Martin 社など主な顧客は、50%以上テストの工数が削減できたことや、早期段階で要求仕様の解析(形式手法による定理証明)をすることで要件上の欠陥を排除し手戻り作業を飛躍的に軽減できたことを公言している

Page 29 29

# Closing Point -複雑になったシステムの安全性の検証と実証は、人手に頼っていては達成できない

- ツールだけでなく、考え方の転換も必要

- どのようにSWが生産されるかも重要

- 検証エンジンがノンリニアなどソフトウェアの要件を満たすことも 重要

- DARPA が直面する課題に対して、経験とノウハウを組入れたツールを提供する

DARPA (Defense Advanced Research Project Agency)

30

Copyright © 2010, T-VEC Technologies, Inc.

- 1. 先見の明、洞察力を持った推進派が必須だが、、、

- 2. 試みは底辺からスマートなエンジニア達によって取組まれることが多いが、実プロジェクトに適合させ調整することを学ぶ時間や予算が十分ではない

- どのようにMDEツールを使うかを決定することが先決(いきなり取り入れない)

- 講習でツールの動作は覚えても、ツールでどのように開発していくかがわからない。

- 3. 検証が容易になるようなモデリング

## Terms and Acronyms

AADL Architecture Analysis & Design Language AP233 Application Protocol 233 ATL ATLAS Transformation Language

BPML Business Process Modeling Language CAD Computer-Aided Design

CASE Computer-Aided Software Engineering

CATIA Computer Aided Three-dimensional Interactive

Application

CDR Critical Design Review

CMM Capability Maturity Model

CMMI Capability Maturity Model Integration CMM Common Warehouse Metamodel

DBMS Database Management System

DoOAF Depart of Defense Architectural Framework

DSL Domain Specific Languages

EMF Eclipse Modeling Framework

EMF Eclipse Modelling Framework

GME Generic Modelling Environment

IBM International Business Machines

ICD Interface Control Document

IEEE Institute of Electrical and Electronics Engineers

INCOSE International Council on Systems Engineering IPR International Organization for Standardization International Organization for Standardization Information Technology JET Java Emiliter Template

LinuxAn operating system created by Linux Torvalds MAP Modeling Adoption Practices

MARTE Modeling and Analysis of Real Time Embedded systems

MATRIXA Product Tamily for model-based control system design

produced by National Instruments

MBT Model Based Testing

MDAN Model Driven Architecture® MDD\* Model Driven Development MDE Model Driven Engineering MDSDModel Driven Software Development **MDSE Model Driven Software Engineering** MIC Model Integrated Computing MMM Modeling Maturity Model

WoDAF United Kingdom Ministry of Defence Architectural Framework MOF Meta Object Facility

MVS Multiple Virtual Storage

NASA National Aeronautics and Space Administration

OCL Object Constraint Language

OMG Object Management Group

OO Object oriented

POR Preliminary Design Review

PIM Platform Independent Model

Pro/E Pro/EMGINEER

PSM Platform Specific Model

QVT Query/View/Transformation

RFP Request for Proposal ROI Return On Investment RTW Mathworks Real Time Workshop

SSCI Systems and Software Consortium

Simulink/Stateflow Product family for model-based control

system produced by The Matthworks

SCR Software Cost Reduction

SDD Software Design Document SOAP A protocol for exchanging XML-based messages

originally stood for Simple Object Access Protocol

Software Factory Term used by Microsoft

SQL Structured Query Language

SRS Software Requirement Specification

SysML System Modeling Language SystemC IEEE Standard 1666 UML Unified Modeling Language XMI XML Metadata Interchange XML eXtensible Markup Language

xUML Executable UML.

Unix An operating system with trademark held by Open Group

VHDL Verilog Hardware Description Language

VGS T-VEC Vector Generation System

VxWorks Operating system owned by WindRiver

31

## **Trademarks**

- OMG®, MDA®, UML®, MOF®, XMI®, SysML™, BPML™ are registered trademarks or trademarks of the Object Management Group.

- . IBM™ is a trademark of the IBM Corporation

- Java™ and J2EE™ are trademark of SUN Microsystems

- XML™ is a trademark of W3C

- BridgePoint is a registered trademark of Mentor Graphics.

- Java is trademarked by Sun Microsystems, Inc.

- MATRIXx is a registered trademark of National Instruments.

- · Real-time Studio Professional is a registered trademark of ARTISAN Software Tools, Inc.

- Rhapsody is a registered trademark of Telelogic/IBM.

- Rose XDE is a registered trademark of IBM.

- SCADE is copyrighted to Esterel Technologies.

- Simulink is a registered trademark of The MathWorks.

- · Stateflow is a registered trademark of The MathWorks.

- Statemate is a registered trademark of Telelogic/IBM.

- T-VEC is a registered trademark of T-VEC Technologies, Inc.

- UNIX is a registered trademark of The Open Group.

- VxWorks is a registered trademark of Wind River Systems, Inc.

- VectorCAST is a trademark of Vector Software.

- Windows is a registered trademark of Microsoft Corporation in the United States and other countries.

- All other trademarks belong to their respective organizations.

32

Copyright © 2010, T-VEC Technologies, Inc.